## An Even harmonic Type Direct Conversion SiGe-MMIC Receiver for W-CDMA Mobile Terminals

Eiji Taniguchi, Mitsuhiro Shimozawa, Takayuki Ikushima†, Keiichi Sadahiro†, Takatoshi Katsura†,

Kenichi Maeda†, Kenji Itoh†, Noriharu Suematsu, Tadashi Takagi and Osami Ishida

Information Technology R&D Center, Mitsubishi Electric Corporation

5-1-1 Ofuna, Kamakura-City, Kanagawa 247-8501, Japan

Tel: +81-467-41-2544 Fax: +81-467-41-2518, e-mail: tania@isl.melco.co.jp

†Mobile Communication Business Division, Mitsubishi Electric Corporation

8-1-1 Tsukaguchi - Honmachi, Amagasaki-City, Hyogo, 661-8661, Japan

**Abstract** — An even harmonic type direct conversion MMIC receiver for W-CDMA mobile terminals in SiGe HBT technology is described. A 2-stage low noise amplifier (LNA) and two self biased anti-parallel diode pairs (APDP's) for even harmonic mixer (EH-MIX) are integrated into a single chip. The LNA is employed dual bias feed circuit to improve the output power and linearity. The EH-MIX can obtain high IIP2 by using APDP. Noise performance of shotky barrier diode (SBD) for APDP fabricated in SiGe process is lower than that of conventional SBD in the market. Both fabricated LNA and EH-MIX demonstrated high RF performances, and they are applicable to RF front-end of W-CDMA mobile terminals.

### I. INTRODUCTION

A Si technology is suitable for mobile terminal applications because of its effectiveness for cost reduction and miniaturization [1]. From the point of view of cost reduction, it has advantage to GaAs technology, especially for mobile terminal application from the quantities of the production. And it enables fully integrated IC called "system on chip" for receiver including RF front-end [2],[3]. But the performance of conventional Si process has been inferior to GaAs for high frequency and low noise applications. The development of SiGe process [4]-[6] having higher RF performances than conventional Si process has allowed us to design lower noise and lower D.C. current drive LNA's suitable for system on chip. We proposed and developed a dual bias feed LNA by using SiGe process and it achieved suitable performance to the W-CDMA terminal application [7].

On the other hands, a direct conversion is focused technology for mobile terminal applications [8]-[10]. It is also effective for cost reduction and miniaturization by eliminating large size IF block, especially SAW filter. But this technology has been difficult to apply to the terminals of mobile communication because of the sensitivity degradation problem due to the second order mixing product (i. e.  $IM_2$ ) and / or self detected LO noise. To

overcome this problem, an EH-MIX employing APDP has been proposed for direct conversion receiver [11]-[13]. Since the frequency of LO signal for the EH-MIX is half of the frequency of RF signal, the LO leakage, which cause self detected LO noise, can be avoided. And the  $IM_2$  is also suppressed by using APDP. We developed EH-MIX with APDP for DCR and it satisfied the requirement of 1.9 GHz-band Personal Handyphone System in Japan [12].

In this paper, an even harmonic type direct conversion SiGe-MMIC receiver is presented for W-CDMA mobile terminals [14] by using 0.5  $\mu$ m SiGe HBT technology. The IC consists of 2-stage LNA and two APDP's for EH-MIX. The LNA employs a dual bias feed circuit [7] which consists of a conventional resistor bias feed and a diode bias feed to prevent the interference of transmit signal leakage.

A Si SBD for APDP fabricated in SiGe process has low noise performance, but relatively low IP3 characteristic due to its low barrier voltage compared with GaAs SBD or Si / Pt SBD. To improve IP3, the APDP employs series connected and area factor optimized SBD. A novel self biased APDP configuration is also adopted to reduce the LO input power dependence of conversion gain [15]. Both fabricated LNA and EH-MIX demonstrate high RF performances, and they are applicable to the RF front-end of W-CDMA mobile terminals.

### II. CONFIGURATION AND DESIGN OF SiGe-MMIC RECEIVER

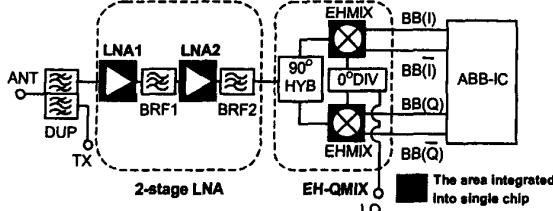

Figure 1 shows the configuration of RF section of direct conversion receiver for W-CDMA mobile terminals. In the direct conversion receiver, 2-stage LNA is employed for improving whole noise performance of the receiver. The 2-stage LNA consists of two LNA's and two band rejection filters (BRF) for transmit signal. And the even harmonic quadrature mixer (EH-QMIX) consists of two

EH-MIX's, a 90 degree hybrid power divider (90° HYB) and an in-phase power divider (0° DIV). The EH-MIX operates by half of receiving signal. The 2-stage LNA and APDPs for EH-MIX are integrated into a single chip as shown in Fig. 1.

Fig. 1. Configuration of RF section of direct conversion receiver for W-CDMA mobile terminals.

#### A. LNA

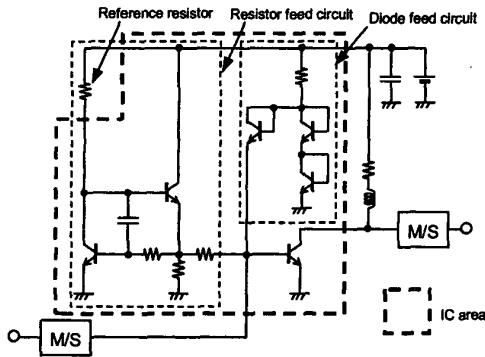

Figure 2 shows the schematic diagram of dual bias feed LNA applied to each 2-stage LNA in direct conversion receiver. For LNA used in frequency-division duplexing system, such as W-CDMA mobile terminals, the performances of high output power and linearity are needed. As shown in Fig. 2, the dual bias feed circuit for base of HBT consists of conventional resistor feed circuit and diode feed circuit. The dual bias feed LNA can improve the performance of output power and linearity compared with conventional one employed only resistor bias feed circuit because the diode feed circuit is regarded as voltage source in large signal region. And the dual bias feed LNA don't need an area consumptive off-chip or on-chip inductor, therefore it is effective for size reduction of RF front-end.

Fig. 2. Schematic diagram of dual bias feed LNA consisting of conventional resistor feed and diode feed circuit for the base. The thick broken line indicates IC area.

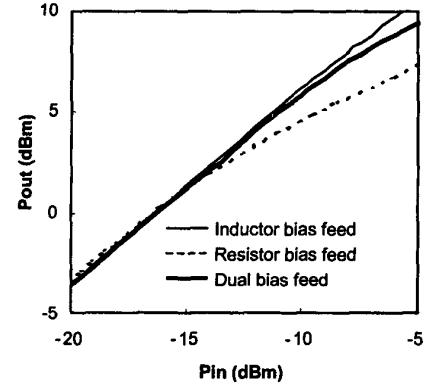

Figure 3 shows the simulated transfer characteristics of LNA's having three different base bias feed circuits. It is verified that the dual bias feed LNA has improved the performance from resistor bias feed LNA. The simulated performances for dual bias feed LNA are summarized in Table I.

Fig. 3. Simulated transfer characteristics of LNA's.

TABLE I Summary of Simulated Performances for 2-Stage LNA (@2.14GHz)

|            | LNA1 | LNA2 |

|------------|------|------|

| Idc (mA)   | 6.1  | 6.1  |

| Gain (dB)  | 15.3 | 16.5 |

| NF (dB)    | 1.3  | 1.5  |

| P1dB (dBm) | 9.8  | 7.5  |

| IIP3 (dBm) | -1.1 | -2.1 |

#### B. EH-MIX

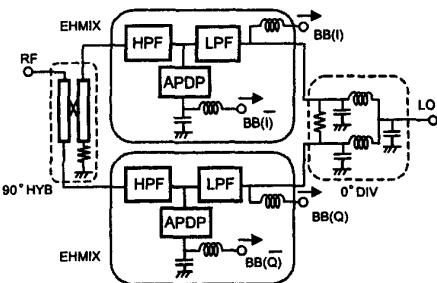

Figure 4 shows the schematic diagram of EH-QMIX including two EH-MIX's which consist of hi-pass / low-pass filters and APDP. The EH-MIX employed APDP is suitable for direct conversion receiver because it can suppress the second order mixing products causing degradation of sensitivity.

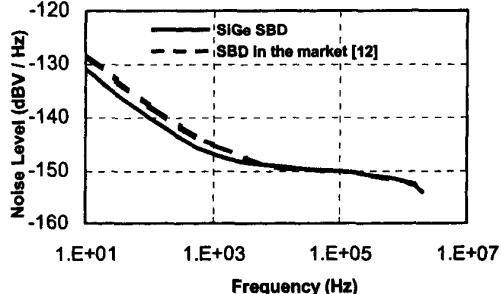

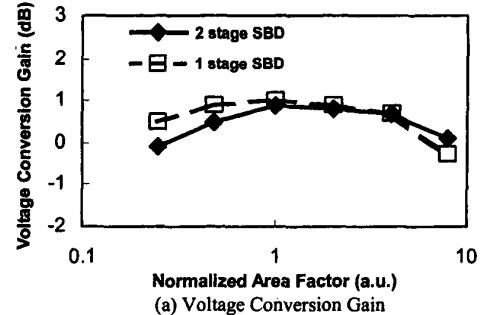

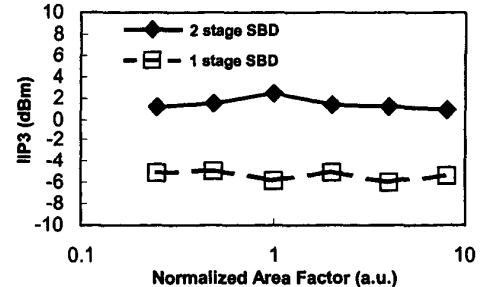

The design of APDP is very important for EH-MIX. The noise performance of Si SBD for APDP fabricated in SiGe process is as low as that of conventional SBD in the market[12] as shown in Fig. 5. But it has relatively low IP3 characteristic due to its low barrier voltage compared with GaAs SBD or Si / Pt SBD. To improve barrier voltage, multi-stage APDP is effective. Figure 6 presents the comparison of voltage conversion gain and IIP3 to normalized area factor of APDP employed 1-stage and 2-

stage SBD by harmonic balance simulation. Each voltage gain and IIP3, shown in Fig. 6, indicates peak value for LO power dependence. It is verified that the APDP employed 2-stage SBD can improve the IIP3, and the conversion gain is almost equivalent compared with 1-stage APDP by setting to reasonable area factor.

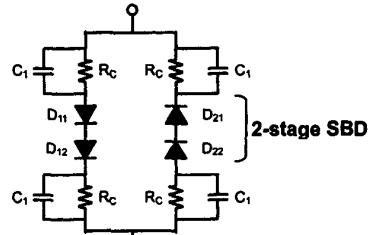

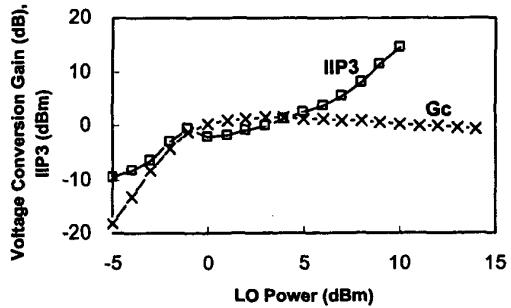

Figure 7 shows the schematic diagram of self biased APDP employed 2-stage SBD for EH-MIX. It has resistances  $R_C$  for self-biasing connected with diode in series and capacitances  $C_1$  that pass RF and LO signals. When LO power is added to these diodes, voltage dropings in D.C. occur in the resistances, and D.C. voltage for biasing arises in LO wave. Increasing LO power, large voltage for self-bias arise, so maximum LO wave voltage adding to diodes is almost constant. Therefore the EH-MIX employed this self biased APDP can reduce the dependence to LO input power of conversion gain. The simulated characteristics of the EH-MIX employed self biased APDP are shown in Fig. 8.

Fig. 4. Schematic diagram of EH-QMIX.

Fig. 5. Comparison of the noise level performance of SBD's

(a) Voltage Conversion Gain

(b) IIP3

Fig. 6. Comparison of voltage conversion gain and IIP3 to normalized area factor of SBD employed 1-stage and 2-stage SBD both by harmonic balance simulation ( $f_{RF}=2100.001$ MHz,  $f_{LO}=1050$ MHz).

Fig. 7. Schematic diagram of self biased APDP employed 2-stage SBD.

Fig. 8. Simulated characteristics of dependence to LO power of voltage conversion gain and IIP3 ( $R_C=400$ ohm,  $R_L=2.7$ kohm).

### III. MEASURED RESULTS

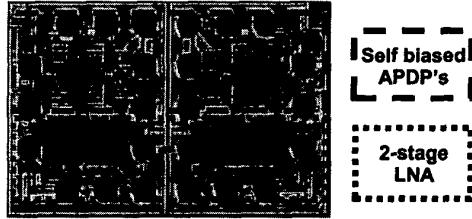

Based on the design, shown in Sec. II, the SiGe-MMIC receiver, which consists of 2-stage LNA (LNA1 and LNA2, not including BRF) and self biased APDP, have been fabricated. The die photograph of fabricated MMIC is shown in Fig. 9. Two LNA's and two self biased APDP's are integrated into a single chip. Each circuit block is electrically separated by grounded metal.

The summary of measured performances for 2-stage LNA and EH-MIX in 2 GHz band are shown in Table II. The measured performances of LNA and EH-MIX include the loss of external circuit such as matching sections and filter circuits.

Fig. 9. The die photograph of fabricated MMIC

(Die size: 1.3 x 2.1mm<sup>2</sup>)

TABLE II

SUMMARY OF MEASURED PERFORMANCES FOR

2-STAGE LNA AND EH-MIX (@2.14GHz)

| 2-Stage LNA |       |

|-------------|-------|

| Idc (mA)    | 12.2  |

| Gain (dB)   | 25.2  |

| NF (dB)     | 2.3   |

| P1dB (dBm)  | +1.7  |

| IIP3 (dBm)  | -13.1 |

| EH-MIX         |     |

|----------------|-----|

| LO Power (dBm) | +6  |

| Gc (dB)        | 1.3 |

| IIP3 (dBm)     | 4.5 |

### IV. CONCLUSION

An even harmonic type direct conversion SiGe-MMIC receiver for W-CDMA mobile terminals has been presented. It consists of 2-stage LNA and two APDPs for EH-MIX. The LNA was employed dual bias feed circuit, which can obtain high output power and linearity. The SBD for APDP was formed into 2-stage to obtain high IIP3 and was employed self biased circuit to reduce the dependence to LO input power of conversion gain. Each LNA and EH-MIX fabricated by 0.5  $\mu$ m SiGe process demonstrated high RF performances applicable to RF front-end of W-CDMA mobile terminals.

### REFERENCES

- [1] Noriharu Suematsu, "On-chip matching Si-MMIC for mobile communication terminal application", 1997 IEEE RFIC Symp., Digest, pp.9-12, June, 1997.

- [2] D. Lovelace, S. Bader, D. Coffing, J. Durec, R. Hester, K. Huehne, E. Main, P. Ovalle, M. Randol, R. Tang, D. Welty, R. Williams and K. Wortel, "Low Cost 900MHz Single-Chip Cordless Telephone Receiver", 2000 IEEE RFIC Symp., Digest, pp.87-90, June, 2000.

- [3] Robert G. Meyer, William D. Mack and Johannes J. E. M. Hageraats, "A 2.5-GHz BiCMOS Transceiver for Wireless LAN's", IEEE Journal of Solid-State Circuits, Vol.32, No.12, pp.2097-2104, December, 1997.

- [4] John D. Cressler, "SiGe HBT Technology: A New Contender for Si-Based RF and Microwave Circuit Applications", IEEE Transactions on Microwave Theory and Techniques, Vol.46, No.5, pp.572-589 May, 1998.

- [5] Rainer Götzfried, Frank Beisswanger, Stephan Gerlach, Andreas Schüppen, Harry Dietrich, Ulrich Seiler, Karl-Heinz Bach and Jens Albers, "RFIC's for Mobile Communication Systems Using SiGe Bipolar Technology", IEEE Transactions on Microwave Theory and Techniques, Vol.46, No.5, pp.661-668 May, 1998.

- [6] Lawrence E. Larson and Michael J. Delaney, "Application of Si/SiGe Technology for High-Speed Communications Systems", 1999 IEEE RFIC Symp., Digest, pp.1077-1080, June, 1999.

- [7] E. Taniguchi, K. Maeda, T. Ikushima, K. Sadahiro, K. Itoh, N. Suematsu and T. Takagi, "Dual Bias Feed SiGe HBT Low Noise Linear Amplifier", 2001 IEEE MTT-S IMS, Digest, pp.285-288, May, 2001.

- [8] A. A. Abidi, "Low-power radio-frequency IC's for portable communications", Proceedings of the IEEE, vol. 83, No. 4, April, 1995.

- [9] C. Takahashi, R. Fujimoto, S. Arai, T. Itakura, T. Ueno, H. Tanimoto, S. Watanabe and K. Hirakawa, "A 1.9GHz Si direct conversion receiver IC for QPSK modulations systems", IEEE International Solid-State Circuits Conference Digest, 1995, pp.138-139.

- [10] T. Tsurumi and T. Maeda, "Design study on a direct conversion receiver front-end for 280MHz, 900MHz and 2.6GHz band radio communication systems", Proceeding of IEEE Vehicular Technology Conference, 1991, pp.457-462.

- [11] S. Sugiyama, N. Suematsu, M. Ono, M. Shimozawa, S. Kubo, K. Itoh, Y. Iyama and O. Ishida, "A 1.9GHz even harmonic type direct conversion Si-MMIC receiver", Proceeding of EuMC, pp.628-632, 1998.

- [12] M. Shimozawa, H. Ikematsu, R. Hayashi, K. Itoh, Y. Isota and O. Ishida, "RF characteristics of an even harmonic type direct conversion receiver for mobile communication", Proceeding of EuMC, pp.633-638, 1998.

- [13] K. Itoh, M. Shimozawa, N. Suematsu and O. Ishida, "Even harmonic type direct conversion receiver ICs for mobile handsets: design challenges and solutions", 1999 IEEE RFIC Symp., Digest, pp.53-56, 1999.

- [14] K. Itoh, et.al., "Integrated Even Harmonic Type Direct Conversion Receiver for W-CDMA Mobile Terminals", this will be presented in 2002 IEEE IMS (Invited).

- [15] M. Shimozawa, et.al., "An Even Harmonic Mixer using Self-Biased Anti-Parallel Diode Pair", this will be presented in 2002 IEEE IMS.